No : Answers Name : Solutions

## Eskişehir Osmangazi University Faculty of Engineering and Architecture

## **Department of Electrical Engineering & Electronics**

"Introduction To VHDL-FPGA" Midterm

Note: Books, notes, computers are allowed, communication of all kind is prohibited. 90 minutes.

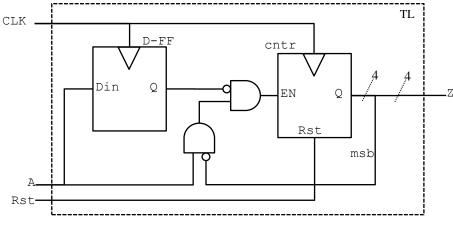

1. Design the following circuit in VHDL within one process. Rst of D-FF is synchronous, cntr is 4 bits up-counter.

```

entity TL is port (

clk, Rst, A : in STD LOGIC;

Z : out STD LOGIC VECTOR(0 to 3));

end TL;

architecture TL of TL is

signal pA : STD LOGIC;

signal cntr : STD LOGIC VECTOR(0 to 3);

begin

process(CLK) is begin

if (rising edge (CLK)) then

pA <= A;

if(Rst='1') then

cntr <= "0000";

elsif((cntr(0)='0')and(pA='0')and(A='1')) then

cntr <= cntr+1;</pre>

end if;

end if;

Z < cntr;</pre>

end process;

end TL;

```

13.11.2025

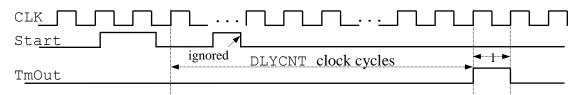

2. A timer-entity accepts a Start input and outputs a delayed TmOut output. Timer detects the falling-edge of the Start input and starts counting at the rising-edge of the clock CLK. When the count reaches generic integer input DLYCNT, the output TmOut is set to '1' for one clock cycle. Start input is ignored when timer is actively counting. Complete timer circuit in VHDL.

```

entity Timer is

generic ( DLYCNT : integer := 1000 );

port (

: in STD LOGIC;

clk

Start : in STD LOGIC;

TmOut : out STD LOGIC);

end Timer;

architecture Timer of Timer is

signal cntr : integer range 0 to DLYCNT := 0;

signal pS : STD LOGIC;

signal counting : STD LOGIC := '0';

begin

process(CLK) is begin

if(rising edge(CLK)) then

pS <= Start;

if(counting='1') then

if(cntr=DLYCNT-1) then

counting <= '0';</pre>

TmOut <= '1';</pre>

else

cntr <= cntr +1;</pre>

end if;

else

TmOut <= '0';</pre>

cntr <= 0;</pre>

if((pS='1') and(Start='0'))

counting <= '1';</pre>

end if;

end if;

end if;

end process;

end Timer;

```

3. Two 4-bits counters up-count in a ping-pong fashion; cntrA counts up, while cntrB waits at 0000. When cntrA reaches 1111, it is set to 0000 and cntrB starts counting while cntrA waits at 0000. When cntrB reaches 1111, it is set to 0000 and cntrA starts counting again while cntrB waits at 0000. This behaviour continues indefinitely. Design the circuit using VHDL.

```

entity TwoCounters is port (

clk : in STD LOGIC;

A, B : out STD LOGIC VECTOR(0 to 3));

end TwoCounters;

architecture TwoCounters of TwoCounters is

signal cntrA, cntrB: STD LOGIC VECTOR(0 to 3);

signal AB : STD LOGIC := '0'; -- which cntr?

begin

A <= cntrA; B <= cntrB;

process(CLK) is begin

if (rising edge (CLK)) then

if (AB = '0') then

if(cntrA="1111") then

cntrA <= "0000";</pre>

AB <= '1';

cntrA <= cntrA +1;</pre>

end if;

else

if(cntrB="1111") then

cntrB <= "0000";

AB <= '0';

else

cntrB <= cntrB +1;</pre>

end if;

end if;

end if;

end process;

end TwoCounters;

```